# Simulavr - an AVR simulation framework version 1.1

Authors and copyright: 2001 - 2020, see Copyright chapter

January 05, 2020

# Contents

| Introduction                       | 1  |

|------------------------------------|----|

| Copyright                          | 3  |

| Features                           | 5  |

| Simple example                     | 7  |

| Example code                       | 7  |

| Run the example                    | 8  |

| Run it with gdb                    | 8  |

| Usage                              | 11 |

| Common options                     | 11 |

| Simulation options                 | 11 |

| GDB options                        | 11 |

| Control options                    | 12 |

| VCD trace options                  | 12 |

| TCL ui option                      | 12 |

| Supported devices                  | 12 |

| Hints                              | 13 |

| Example usage                      | 13 |

| Tracing                            | 14 |

| Download                           | 17 |

| Secure download                    | 17 |

| Release files                      | 17 |

| Debian packages                    | 17 |

| Documentation                      | 17 |

| Tarball's                          | 18 |

| Old binary packages                | 18 |

| Building and Installing            | 19 |

| Prerequisites                      | 19 |

| Build                              | 20 |

| Targets                            | 20 |

| Debian packages                    | 21 |

| Install                            | 21 |

| Build using docker                 | 22 |

| Step 1: create a docker image      | 22 |

| More examples                      | 25 |

| Simple Example                     | 25 |

| TCL Examples                       | 25 |

| TCL Anacomp Example                | 26 |

| LCD and SerialRx, SerialTx Example | 27 |

| Keyboard and SerialRx Example      | 28 |

| atmega128_timer example                   | 29 |

|-------------------------------------------|----|

| atmega48 example                          | 30 |

| feedback example                          | 31 |

| Python examples                           | 32 |

| Simple timer unittest                     | 32 |

| Connect pins and change state             | 33 |

| How to control pins                       | 34 |

| How to get a more detailed view           | 34 |

| Multicore example                         | 35 |

| ADC example                               | 36 |

| Verilog examples                          | 37 |

| baretest example                          | 37 |

| loop example                              | 38 |

| spi waveform examples                     | 38 |

| vst example                               | 39 |

| spc example                               | 40 |

| Graphic User Interface with TCL           | 41 |

| Details of the example GUI                | 41 |

| UpdateControl                             | 41 |

| Net                                       | 41 |

| AnalogNet                                 | 42 |

| LCD                                       | 42 |

| Keyboard                                  | 43 |

| SerialRx / SerialTx                       | 43 |

| Scope                                     | 43 |

| Command Line Parameter -u vs. Interpreter | 43 |

| The VPI interface to Verilog              | 45 |

| Usage                                     | 45 |

| Example iverilog command line             | 45 |

| Bugs and particularities                  | 46 |

| Limitations                               | 47 |

| Overall Limitations                       | 47 |

| CPU Limitations                           | 47 |

| Help Wanted                               | 49 |

| License                                   | 51 |

# Introduction

The SimulAVR program is a simulator for the Atmel AVR family of microcontrollers. Atmel was taken over by Microchip in the year 2016.

SimulAVR can be used either standalone or as a remote target for avr-gdb. When used in gdbserver mode, the simulator is used as a back-end so that avr-gdb can be used as a source level debugger for AVR programs.

SimulAVR started out as a C based project written by Theodore Roth. The hardware simulation part has since been completely re-written in C++. Only the instruction decoder and the avr-gdb interface are mostly copied from the original simulavr sources. This C++ based version was known as simulavrxx until it became feature compatibile with the old simulavr code, then it renamed back to simulavr.

The core of SimulAVR is functionally a library. This library is linked together with a command-line interface to create a command-line program. It is also linked together with interpreter interfaces to create libraries that can be used by a interpreter language (currently Python / TCL). In the examples directory there are examples of simulations with a graphical environment (with the Tcl/Tk interface) or how to write for example unit tests by using Python interface. The graphic components in Tcl/Tk examples do not show any hardware / registers of the simulated CPU. It shows only external components attached to the IO-pins of the simulated CPU.

# Copyright

Authors:

- 2001, 2002, 2003 Theodore A. Roth

- 2004 Theodore A. Roth, Klaus Rudolph

- 2005 Klaus Rudolph

- 2008 Knut Schwichtenberg

- 2009 Joel Sherrill, Onno Kortmann, Thomas Klepp

- 2010 2014 Petr Hluzin and others

Permission is granted to make and distribute verbatim copies of this manual provided the copyright notice and this permission notice are preserved on all copies.

Permission is granted to copy and distribute modified versions of this manual under the conditions for verbatim copying, provided that the entire resulting derived work is distributed under the terms of a permission notice identical to this one.

Permission is granted to copy and distribute translations of this manual into another language, under the above conditions for modified versions, except that this permission notice may be stated in a translation approved by the Free Software Foundation.

# **Features**

What features are new:

- Run multiple AVR devices in one simulation. (only with interpreter interfaces or special application linked against simulavr library) Multiple cores can run where each has a different clock frequency.

- Connect multiple AVR core pins to other devices like LCD, LED and others. (environment)

- Connect multiple AVR cores to multiple avr-gdb instances. (each on its own socket/port number, but see first point for running multiple AVR cores)

- Write simulation scripts in Tcl/Tk or Python, other languages could be added by simply adding swig scripts!

- Tracing the execution of the program, these traces support all debugging information directly from the ELF-file.

- The traces run step by step for each device so you see all actions in the multiple devices in time-correct order.

- Every interrupt call is visible.

- Interrupt statistics with latency, longest and shortest execution time and some more.

- There is a simple text based UI interface to add LCD, switches, LEDs or other components and can modify it during simulation, so there is no longer a need to enter a pin value during execution. (Tcl/Tk based)

- Execution timing should be nearly accurate, different access times for internal RAM / external RAM / EEPROM and other hardware components are simulated.

- A pseudo core hardware component is introduced to do "printf" debugging. This "device" is connected to a normal named UNIX socket so you do not have to waste a UART or other hardware in your test environment. (How?)

- ELF-file loading is supported, no objcopy needed anymore.

- Execution speed is tuned a lot, most hardware simulations are now only done if needed.

- External IO pins which are not ports are also available. (E.g. ADC7 and ADC8 on ATmega8 in TQFP package.)

- External I/O and some internal states of hardware units (link prescaler counter and interrupt states) can be dumped out into a VCD trace to analyze I/O behavior and timing. Or you can use it for tests.

Simple example

# Simple example

Lets look on a simple example to demonstrate the power of simulavr.

## **Example code**

Assume, that we have written a small program for a ATtiny2313 controller. (this example code is taken from examples/simple\_ex1) Save it as simple.c:

```

/* This port corresponds to the "-W 0x20,-" command line option. */

#define special output port (*((volatile char *)0x20))

/* This port corresponds to the "-R 0x22,-" command line option. */

#define special input port (*((volatile char *)0x22))

/* Poll the specified string out the debug port. */

void debug_puts(const char *str) {

const char *c;

for(c = str; *c; c++)

special output port = *c;

}

/* Main for test program. Enter a string and echo it. */

int main() {

volatile char in char;

/* Output the prompt string */

debug puts("\nPress any key and enter:\n> ");

/* Input one character but since line buffered, blocks until a CR. */

in char = special input port;

/* Print the "what you entered:" message. */

debug puts("\nYou entered: ");

/* now echo the rest of the characters */

do {

special output port = in char;

} while((in char = special input port) != '\n');

special output port = '\n';

special output port = ' n';

return 0;

}

```

What does this code do:

```

#define special_output_port (*((volatile char *)0x20))

#define special_input_port (*((volatile char *)0x22))

```

This two preprocessor lines define 2 virtual port register, one for reading a character, one for writing a character. Think about it as the data in/out register of a UART unit. But instead to receive/send characters by transmission line you get it from stdin/pipe or write it to stdout/pipe. This is a feature of simulavr to have a simple possibility to debug your code

void debug\_puts(const char \*str) { ... }

This defines a function 'debug\_puts', which gets a char string and puts it out to our special "UART"

```

/* Input one character but since line buffered, blocks until a CR. */

in char = special input port;

```

In this line we wait for the first character from stdin/pipe ...

```

/* now echo the rest of the characters */

do {

special_output_port = in_char;

} while((in_char = special_input_port) != '\n');

```

and then put the received character to stdout/pipe and receive the next character until we receive a newline. After this we leave main. (not recommended for production code!)

Now we compile and link this code with avr-gcc:

```

> avr-gcc -g -02 -mmcu=attiny2313 -o simple.elf simple.c

```

### **Run the example**

We start simulation with:

```

> simulavr -d attiny2313 -f simple.elf -W 0x20,- -R 0x22,- -T exit

Press any key and enter:

> abcdef

You entered: abcdef

>

```

What's happen:

- we start simulation for a ATtiny2313 with our program 'simple.elf'

- we create a write pipe to stdout at register 0x20

- we create a read pipe from stdin at register 0x22

- we end simulation, if exit label is arrived (exit label will automatically inserted by avr-gcc, this is the next address after calling main function and means, that we left main function)

- our input is "abcdef" followed by enter

- we got back "abcdef"

### Run it with gdb

Now lets start a debug session.

At first we have to start the simulation:

```

> simulavr -d attiny2313 -f simple.elf -g

Going to gdb...

Waiting on port 1212 for gdb client to connect...

```

It's quite similar to the call above. We tell simulavr, that we use ATtiny2313, that our program is simple.elf and - that's new - that we start a gdb session. As you can see, simulavr opens port 1212 and wait for connection from gdb.

Now we have to open a new shell and start avr-gdb:

```

> avr-gdb

GNU gdb 6.4

Copyright 2005 Free Software Foundation, Inc.

GDB is free software, covered by the GNU General Public License, and you are

welcome to change it and/or distribute copies of it under certain conditions.

Type "show copying" to see the conditions.

There is absolutely no warranty for GDB. Type "show warranty" for details.

This GDB was configured as "--host=i486-linux-gnu --target=avr".

(gdb)

```

(gdb) is the input prompt and avr-gdb waits now for commands:

```

(qdb) file simple.elf

Reading symbols from /home/.../simple.elf...done.

(gdb) target remote localhost:1212

Remote debugging using localhost:1212

0x00000000 in vectors ()

(gdb) load

Loading section .text, size 0xba lma 0x0

Loading section .data, size 0x58 lma 0xba

Start address 0x0, load size 274

Transfer rate: 2192 bits in <1 sec, 137 bytes/write.

(qdb) step

Single stepping until exit from function vectors,

which has no line number information.

0x0000001a in trampolines start ()

(qdb) quit

The program is running. Exit anyway? (y or n) y

>

```

file simple.elf

load our program into debugger

target remote localhost:1212

now we connect us to simulavr, in shell with simulavr we can see now, that simulavr has connection to gdb: Connection opened by host 0.0.0.0, port 1212.

load

now we load our program to simulavr

step

we make here a single step, but now you're able to debug your code as you like

quit

for now we close our debug session

After closing our debug session we have to stop simulavr by typing  $\sim$  in this shell with simulavr running. Otherwise simulavr waits for a next gdb session.

Usage

Invoke simulavr:

> simulavr {options}

## **Common options**

-V, --version print out version and exit immediately

-h, --help

print this help

-v, --verbose

output some hints to console

# **Simulation options**

- -d <name>, --device <name>

simulate device <name>, see below for simulated devices

- -f <name>, --file <name>

load elf-file <name> for simulation in simulated target

- -F <Hz>, --cpufrequency <Hz> set the cpu frequency to <Hz>

- -t <file>, --trace <file>

enable trace outputs to <file>

- -s, --irqstatistic prints statistic informations about irq usage after simulation is stopped

- -C <name>, --core-dump <name>

dump a core memory image <name> to file on exit

# **GDB** options

- -g, --gdbserver listen for GDB connection on TCP port defined by -p

- -G, --gdb-debug listen for GDB connection and write debug info

- --gdb-stdin for use with GDB as 'target remote | ./simulavr'

- -p <port>

use <port> for gdb server (default is port 1212)

-n, --nogdbwait

do not wait for gdb connection

# **Control options**

- -m <nanoseconds>

maximum run time of <nanoseconds>

- -W <offset\_file>, --writetopipe <offset\_file>

add a special pipe register to device at IO-Offset and opens file for writing, write argument as

'offset,file', file can be '-' to write to standard output

- -R <offset\_file>, --readfrompipe <offset\_file> add a special pipe register to device at IO-Offset and opens file for reading, write argument as 'offset,file', file can be '-' to write to standard input

- -a <offset>, --writetoabort <offset>

add a special register at IO-offset which aborts simulator run

- -e <offset>, --writetoexit <offset>

add a special register at IO-offset which exits simulator run

- -T <label>, --terminate <label> stops simulation if PC runs on <label>, <label> is a text label or a address

- -B <label>, --breakpoint <label> same as -T for backward compatibility

#### - M

disable messages for bad I/O and memory references

-l <number>, --linestotrace <number>

maximum number of lines in each trace file. 0 means endless. Attention: if you use gdb & trace,

please use always 0!

# VCD trace options

-c <tracing-option>

Enables a tracer with a set of options. The format for <tracing-option> is: <tracer>[:further-options ...]

-o <trace-value-file>

Specifies a file into which all available trace value names will be written. Use '-' for standard output

# **TCL ui option**

-u

run with user interface for external pin handling at port 7777

## **Supported devices**

- at90can128 atmega1284 atmega168 atmega48 atmega8 at90can32 atmega1284a atmega2560 • atmega64

- at90can64

- at90s4433

- at90s8515

- atmega128

- atmega1280

### Hints

Option -d

The option -d is mandatory, if an elf file isn't given or elf file dosn't contain device signature. To put device signature to elf file you can insert the following line to your source code (but only once!):

#include <avr/signature.h>

If this option is given and device signature will be found in elf file, then the given signature by device name is compared to signature in elf file. If this isn't equal, then simulavr stops with an error message.

Attention: some devices doesn't support all peripheral parts of controller. (for example CAN peripheral in at90can... devices) Ports and timer are mostly implemented.

GDB option -g

Do not run simulavr with -g-option unattended and also not with admin rights. This could be a security hole for your system!

GDB option -G

Use it as a alternative to option -g. This is only useful, if you want to see, what data is sent from gdb to simulavr and back!

#### Options -R / -W / -a / -e

The commands -R / -W / -a / -e are not AVR-hardware related. Here you can link an address within the address space of the AVR to an input or output pipe. This is a simple way to create a "printf"debugger, e.g. after leaving the debugging phase and running the AVR-Software in the simulator or to abort/exit a simulation on a specified situation inside of your program. For more details see the example in the directory examples/simple ex1 or here.

## **Example usage**

Using the simulator with avr-gdb is very simple. Start simulavr with:

simulavr -g

Now simulavr opens a socket on port 1212. If you need another port give the port number with:

simulavr -p5566

which will start simulavr with avr-gdb socket at port 5566.

After that you can start avr-gdb or ddd with avr-gdb:

avr-gdb

- atmega1284p

- atmega16

atmega164a

atmega164p

- atmega164

- atmega32

- atmega324

- atmega324a

- atmega324p

- atmega328

- atmega640

- atmega644

- atmega644a

- atmega644p

- atmega88

- attiny2313

- attiny25

- attiny45

- attiny85

13

```

Tracing

```

or:

ddd --debugger avr-gdb

In the comandline of ddd or avr-gdb you can now enter your debug commands:

```

file a.out

target remote localhost:1212

load

step

step

....

quit

```

Attention: In the actual implementation there is a known bug: If you start in avr-gdb mode and give no file to execute -f filename you will run into an "Illegal Instruction". The reason is that simulavr runs immediately with an empty flash. But avr-gdb is not connected and could stop the core. Solution: Please start with simulavr -g -f <filename>. The problem will be fixed later. It doesn't matter whether the filename of the simulavr command line is identical to the filename of avr-gdb file command. The avr-gdb downloads the file itself to the simulator. And after downloading the core of simulavr will be reset complete, so there is not a real problem.

## Tracing

One of the core features is tracing one or multiple AVR cores in the simulator. To enable the trace feature you have simply to add the -t option to the command line. If the ELF-file you load into the simulator has debug information the trace output will also contain the label information of the ELF-file. This information is printed for all variables in flash, RAM, ext-RAM and also for all known hardware registers. Also all code labels will be written to the trace output.

What is written to trace output:

| 2000 a.out 0x0026: |                                                        |       |

|--------------------|--------------------------------------------------------|-------|

| 2250 a.out 0x0028: | do_copy_data+0x1 LDI R26, 0x60 R26=0x60 X=0x0060       |       |

| 2500 a.out 0x002a: | do_copy_data+0x2 LDI R27, 0x00 R27=0x00 X=0x0060       |       |

| 2750 a.out 0x002c: | do copy data+0x3 LDI R30, 0x22 R30=0x22 Z=0x0022       |       |

|                    | docopy_data+0x4 LDI R31, 0x01 R31=0x01 Z=0x0122        |       |

| 3250 a.out 0x0030: | do_copy_data+0x5                                       |       |

| 3500 a.out 0x0038: | .do_copy_data_start CPU-waitstate                      |       |

| 3750 a.out 0x0038: | .do_copy_data_start CPI R26, 0x60 SREG=[Z-]            |       |

| 4000 a.out 0x003a: | .do_copy_data_start+0x1 CPC R27, R17 SREG=[Z-]         |       |

| 4250 a.out 0x003c: | SP_L BRNE ->0x0032 .do_copy_data_loop                  |       |

|                    | SREG,SP_H,doclear_bss LDI R17, 0x00 R17=0x00           |       |

| 4750 a.out 0x0040: | SREG,SP_H,do_clear_bss+0x1 LDI R26, 0x60 R26=0x60 X=0> | <0060 |

| 5000 a.out 0x0042: |                                                        | <0060 |

| 5250 a.out 0x0044: | SREG,SP_H,doclear_bss+0x3 RJMP 48                      |       |

|                    | .do_clear_bss_start CPU-waitstate                      |       |

What the columns mean:

- absolute time value, it is measured in nanoseconds (ns)

- the code you simulate, normally shown as the file name of the loaded executable file. If your simulation runs multiple cores with multiple files you can see which core is stepping with which instruction.

- actual PC, meaning bytes not instructions! The original AVR documentation often writes in instructions, but here we write number of flash bytes.

- label corresponding to the address. The label is shown for all known labels from the loaded ELF-file. If multiple labels are located to one address all labels are printed. In future releases it is

maybe possible to give some flags for the labels which would be printed. This is dependent on the ELF-file and BFD-library.

- after the label a potential offset to that label is printed. For example main+0x6 which means 6 instructions after the main label is defined.

- The decoded AVR instruction. Keep in mind pseudo-opcodes. If you wonder why you write an assembler instruction one way and get another assembler instruction here you have to think about the Atmel AVR instruction set. Some instructions are not really available in the AVR-core. These instructions are only supported for convenience (i.e. are pseudo-ops) not actual opcodes for the hardware. For example, CLR R16 is in the real world on the AVR-core EOR R16, R16 which means exclusive or with itself which results also in zero.

- operands for the instruction. If the operands access memory or registers the actual values of the operands will also be shown.

- If the operands access memory (Flash, RAM) also the labels of the accessed addresses will be written for convenience.

- If a register is able to build a special value with 16 bits range (X,Y,Z) also the new value for this pseudo register is printed.

- If a branch/jump instruction is decoded the branch or jump target is also decoded with the label name and absolute address also if the branch or jump is relative.

- A special instruction @command{CPU-waitstate} will be written to the output if the core needs more then one cycle for the instruction. Sometimes a lot of wait states will be generated e.g. for eeprom access.

- if the status register is affected also the SREG=[-----Z-] is shown.

Attention: If you want to run the simulator in connection to the avr-gdb interface and run the trace in parallel you have to keep in mind that you MUST load the file in avr-gdb and also in the simulator from command-line or script. It is not possible to transfer the symbols from the ELF-file through the avr-gdb interface. For that reason you always must give the same ELF-file for avr-gdb and for simulavr. If you load another ELF-file via the avr-gdb interface to the simulator the symbols for tracing could not be updated which means that the label information in the trace output is wrong. That is not a bug, this is related to the possibilities of the avr-gdb interface.

# Download

Project homepage is available at https://savannah.nongnu.org/projects/simulavr. There you'll find also a link to download area. If you want to download other versions, please use the link to download area!

## Secure download

#### Note

Replace X.Y.Z with the real release, this is for example 1.1.0.

Releases are secured by gpg signatures. For every package, tarball, document, which you can download here, you'll find a signature file too. This is a cryptographic checksum over the released file and helps you to find out, if this file is unchanged by somebody unauthorized.

For this, you need a gpg installation and our gpg keyring. Download this keyring and import it to your keyring:

> gpg --import simulavr-keyring.gpg

You can list out, what's now in your keyring:

> gpg --list-keys

After you have downloaded release file (tarball, document, binary package) together with the signature file, you can verify, that your download is correct (for example, you've downloaded simulavr-X.Y.Z.tar.gz.together with simulavr-X.Y.Z.tar.gz.sig):

> gpg --verify simulavr-X.Y.Z.tar.gz.sig

If there is no message, that file is invalid, you can use your downloaded file. (of course, you can use it also without verifying signature, but on your own risk!)

# **Release files**

#### Debian packages

| Package                                                   | Release date       |

|-----------------------------------------------------------|--------------------|

| simulavr-vpi_1.1.0_amd64.deb (42K) and gpg signature      | Jan 05 2020, 17:07 |

| simulavr-tcl_1.1.0_amd64.deb (238K) and gpg signature     | Jan 05 2020, 17:07 |

| simulavr-dev_1.1.0_amd64.deb (103K) and gpg signature     | Jan 05 2020, 17:07 |

| simulavr_1.1.0_amd64.deb (95K) and gpg signature          | Jan 05 2020, 17:04 |

| python3-simulavr_1.1.0_amd64.deb (611K) and gpg signature | Jan 05 2020, 17:04 |

| libsim_1.1.0_amd64.deb (364K) and gpg signature           | Jan 05 2020, 17:03 |

### Documentation

| Package                                                        | Release date       |

|----------------------------------------------------------------|--------------------|

| manual-1.1.0-rc1.pdf (1M) and gpg signature                    | Dec 04 2019, 16:59 |

| manual-1.1.0.pdf (1M) and gpg signature                        | Jan 05 2020, 17:03 |

| simulavr-1.1.0-api-documentation.tar.gz (4M) and gpg signature | Jan 05 2020, 17:05 |

| simulavr-1.1.0-html-manual.tar.gz (457K) and gpg signature     | Jan 05 2020, 17:06 |

| manual-1.0.pdf (1M) and gpg signature                          | Feb 12 2012, 16:29 |

| simulavr-1.0-api-documentation.tar.gz (194M) and gpg signature | Feb 12 2012, 19:37 |

## Tarball's

| Package                                                                                                                                                  | Release date                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| simulavr-1.0.0.tar.gz (989K) and gpg signature                                                                                                           | Feb 12 2012, 19:41                                             |

| simulavrxx-0.8.006.tar.gz (541K) and gpg signature                                                                                                       | Jul 30 2005, 03:46                                             |

| simulavrxx-0.8.005.tar.gz (511K) and gpg signature                                                                                                       | Feb 09 2005, 03:29                                             |

| simulavrxx-0.8.004.tar.gz (415K) and gpg signature                                                                                                       | Nov 11 2004, 06:41                                             |

| simulavrxx-0.8.003.tar.gz (320K) and gpg signature                                                                                                       | Aug 25 2004, 22:47                                             |

| simulavr-0.1.2.1.tar.bz2 (351K) and gpg signature                                                                                                        | Jan 19 2004, 00:08                                             |

| simulavr-0.1.2.2.tar.gz (446K) and gpg signature                                                                                                         | Feb 16 2005, 23:42                                             |

| simulavr-0.1.2.3.tar.gz (468K) and gpg signature                                                                                                         | Jan 07 2008, 21:50                                             |

| simulavr-0.1.2.4.tar.gz (468K) and gpg signature                                                                                                         | Mar 09 2008, 20:39                                             |

| simulavr-0.1.2.5.tar.gz (469K) and gpg signature                                                                                                         | Mar 16 2008, 21:31                                             |

| simulavr-0.1.2.6.tar.gz (469K) and gpg signature                                                                                                         | Mar 05 2009, 09:30                                             |

| simulavr-0.1.2.7.tar.gz (484K) and gpg signature                                                                                                         | Jul 03 2011, 09:22                                             |

| simulavr-0.1.2.tar.bz2 (338K) and gpg signature                                                                                                          | Jan 18 2004, 05:24                                             |

| simulavr-0.1.2.5.tar.gz (469K) and gpg signature<br>simulavr-0.1.2.6.tar.gz (469K) and gpg signature<br>simulavr-0.1.2.7.tar.gz (484K) and gpg signature | Mar 16 2008, 21:31<br>Mar 05 2009, 09:30<br>Jul 03 2011, 09:22 |

# Old binary packages

| Package                                                        | Release date       |  |

|----------------------------------------------------------------|--------------------|--|

| simulavr-1.0.0-binary-linux32.tar.gz (16M) and gpg signature   | Feb 12 2012, 19:40 |  |

| simulavr-1.0.0-binary-win7-32bit.tar.gz (6M) and gpg signature | Feb 13 2012, 19:38 |  |

|                                                                |                    |  |

# **Building and Installing**

#### Note

Examples in this chapter refer to a version X.Y.Z, please replace this with your current version, for example 1.1.0!

This chapter describes, how you can build and install simulavr.

### Attention!

The build scripts with cmake aren't prepared to work with Windows or Mac OS, even if cmake itself is able to create build configuration for this platforms!

# Prerequisites

To build simulavr only you need:

- cmake (at least version 3.5 or newer)

- make

- gcc (at least a version, which supports c++11)

- git

- python (at least version 3.5 or newer)

If you want to build the python extension, you need also python development files (e.g. in a debian or ubuntu platform you have to install python3-dev package) and swig. (at least version 3.x or newer)

If you want to build tcl extension, you need:

- tclsh

- tcl development files

- swig (at least version 3.x or newer)

To build the verilog extension you have to install iverilog tool. (included vvp)

For running the complete regression test you need also:

- avr-gcc (on debian it's package gcc-avr)

- avr-libc

• valgrind (optional, check for overwriting memory and memory leaks) Building the documentation suite needs also:

- gzip

- help2man

- makeinfo

- doxygen (optional, for api documentation)

- dot (optional, for api documentation)

- python module sphinx (at least version 2.2 for web site and manual)

- python module rst2pdf (at least version 0.94 for web site and manual)

Build

- python module beautifulsoup4 (short bs4, for web site and manual)

- python module requests (for web site and manual)

Building debian packages need also:

- dpkg

- strip

- fakeroot

# **Build**

simulavr uses cmake and git. This means that you should be able to use the following steps to build simulavr:

```

> git clone https://git.savannah.nongnu.org/git/simulavr.git

```

> cd simulavr

> make build

> make check

This will build simulavr and check, if the main function is ok.

In the root directory of repository you can find a Makefile as wrapper for calling cmake and control configuration. If you call:

> make

you'll get a help, what targets are available and what the targets will do.

### Targets

make cfgclean

Removes the build directory. The make wrapper configures cmake for "out of source" build. E.g. nearly all build artifacts are below build directory. This removes also the complete cmake configuration.

make clean

As usual, it removes all build artifacts but let cmake configuration untouched.

make build

Build simulavr and all extensions as configured.

make check

Run regression test.

make doc

Build documentation, e.g. man page, info page, sphinx documentation (manual and web site).

make doxygen

Build api documentation.

make debian

Build debian packages for simulavr tool and lib and all configured extensions.

To switch on/off configuration options, you have to call make with the configuration target:

> make debug # build program, libs and extensions with debug information > make no-debug # build without debug information

Other config targets are:

• python (build/do not build python module)

- tcl (build/do not build tcl module)

- verilog (build/do not build verilog extension)

- valgrind (run the gtest regression test additional with valgrind for memory check)

With target all and simple you can switch on and off all configuration options together. There is one special target, taken over from old automake build system:

> make keytrans

This create keytrans.h for tcl extension.

## **Debian packages**

To support install on debian systems (e.g. debian and ubuntu and derivates) it's possible to build debian packages. Go to root directory and call:

> make debian

This will produce the following packages (PLAT represents the build platform):

libsim\_X.Y.Z\_PLAT.deb

The simulavr lib itself.

simulavr\_X.Y.Z\_PLAT.deb

The simulavr tool, depends on libsim package.

simulavr-dev\_X.Y.Z\_PLAT.deb

Contains header and other files, to build applications against libsim, depends on libsim package.

simulavr-vpi\_X.Y.Z\_PLAT.deb

Verilog extension, depends on libsim package.

python3-simulavr\_X.Y.Z\_PLAT.deb

Python3 module, static linked, so no other dependencies needed.

```

simulavr-tcl_X.Y.Z_PLAT.deb

```

Tcl extension, depends on libsim package.

On a debian system you could install the simulavr tool itself then (you need root permission):

```

cd <root_of_repo>/build/debian

apt install libsim_X.Y.Z_PLAT.deb # first install lib to fullfil dependencies

apt install simulavr_X.Y.Z_PLAT.deb

```

After that you can check, if simulavr is ready:

simulavr -h

### Install

If you want to make a installation on a system and not use debian packages, (maybe you system doesn't support debian packages) then you can call the install target from cmake itself after the normal build is finished:

```

cd <root_of_repo>

cmake --build build --target progdoc

cmake --build build --target install

```

After that you'll find the install tree in the build/install directory. Copy this to the destination, as you want. As example (you need root permission):

```

cd <root_of_repo>/build/install

cp -r usr /

```

# **Build using docker**

If docker is installed, then you can create docker images to build simulavr in a stable and defined environment and independent from what's installed on your computer.

#### Step 1: create a docker image

There are docker scripts and a small script to create a image:

```

cd <root_of_repo>/docker

./mkimage buildscripts/bionic.build.Dockerfile

```

This will create a docker image with name "simulavrbuild" and version "bionic". (e.g. Ubuntu 18:04)You can check it with:

docker images

There you should find the new created image in the list. Attention: because of the installed packages in this image, the resulting image size is about 1G! There is also a docker script for ubuntu 16:04, called "xenial.build.Dockerfile".

Now, after the image is ready, you can create the build container:

```

docker run -it -u buildbudy --name <container_name> simulavrbuild:bionic

buildbudy@e1694c8b9f26:/

```

You stay now in your new created container, the second line is the bash prompt. You have created a container with name "<container\_name>" (replace this to a name, which is useful for you!) from the new built image and running with user "buildbudy". If you omit the "-u" option, then you'll be root inside your container. Because this could be dangerous in some cases and normally not needed, it's better to run with a normal user with normal privileges also inside the container!

You can now leave the container on every time with "exit" command and come back with:

docker start -i <container\_name>

In this container you can now start the build:

```

cd # to come to buildbudy's home directory

git clone -b master https://git.savannah.nongnu.org/git/simulavr.git simulavr

cd simulavr

make all # to switch on all config options exept debug option

make build

```

After that is finished, you've build sucessful simulavr and all extensions.

If you don't want to clone from official repository, as described before, you could also clone from a local repository (maybe where you've written some new code). In this case the container have to created with a extra option:

docker run -it -u buildbudy --name <container\_name> -v /local/path:/repo simulavrbuild:bion:

Replace (as before) "<container\_name> with a useful name and /local/path with a path, where your local repository is hold. For example /home/user/simulavr is the repository, then ypu could give "-v /home/user:/repo". Inside the container you will find then a new directory /repo, where you see your repository. Then the clone command could be:

cd

git clone -b your\_branch /repo/simulavr simulavr\_local

To get out your build artefacts, you can user "docker cp" command (and after you leaved the container):

```

docker cp <container_name>:/home/buildbudy/simulavr/build/app/simulavr .

docker cp <container_name>:/home/buildbudy/simulavr/build/libsim/libsim.so .

```

This copies the simulavr tool itself and the simulavr library, which is needed, simulavr to run.

# **More examples**

Simulavr is designed to interact in a few different ways. These examples briefly explain the examples that can be found in the source distribution's examples directory.

## Simple Example

This sample uses only simulavr to execute a hacked AVR program. I say "hacked" because is shows using 3 simulator features that provide input, output and simulation termination based on "magic" port access and reaching a particular symbol. It is only really useful for getting your feet wet with simulavr, it is not a great example of how to use simulavr. It is thought to be useful enough to the absolute newbie to get you started though. See here for a more detailed information.

Go to examples/simple\_ex1 and build there the avr program:

```

> avr-gcc -g -02 -mmcu=at90s8515 -o fred.elf fred.c

```

After performing the build, run it. Notice the use of -W, -R and -T flags:

> simulavr -d at90s8515 -f fred.elf -W 0x20,- -R 0x22,- -T exit

Then type something followed by **ENTER**. Your typed string will be printed out. For explanation of simulavr options see usage.

## **TCL Examples**

There are examples, which use TcI/Tk. For that you must also install Itcl package for your Tcl. It will be used in all examples with Tcl and a Tk GUI! Over that you can find also examples for python interface and for the verilog module.

The anacomp example is all we have started with. Anacomp brings up an Itcl based GUI which shows two analog input simulations, a comparison output value, and a toggle button on bottom. After changing the inputs, hit the corresponding update to clock the simulation to respond to the changed inputs.

The avr-gdb session for me requires a "load" before hitting "continue", which actually starts the simulation.

It is strongly recommended to implement own simulation scripts very closely to the examples. Usage of a different name than .x for the grahic frame need changes of gui.tcl as well as some simulavr sources. So stay better close to the example.

To use the TCL examples you have to prepare 2 files in :file:`examples` directory!

In examples directory you can find 2 files: simulavr.tcl.sample and gui.tcl.sample Copy this files to simulavr.tcl and gui.tcl and edit the copied files.

Edit simulavr.tcl:

You need before 3 file paths, the path from tclsh tool, the path from wish tool (both from the TCL/TK suite) and the path, where your TCL extention for simulavr is installed. You can find out the paths for tclsh and wish with the following commands:

> which tclsh # prints out the path for tclsh, if found > which wish # prints out the path for wish, if found

Later you need also the ddd debugger graphical interface to avr-gdb:

> which ddd # prints out the path for ddd, if found

For the path, where libsimulavr.so (the TCL extension) is installed, you have to seek, where it's installed. This is system dependend! On debian systems and if you have made the install with debian packages, it would be: /usr/lib/simulavr/libsimulavr.so, that means, that you have to choose /usr/lib/simulavr.

Then edit the beginning of file simulavr.tcl:

```

#! @TCL_SHELL@

# configuration area

set WishCMD "@TCL_WISH@"

set buildPrefix "@prefix@"

# end configuration area

#

#

# This demonstrates how to implement a custom Tcl "main" for the

...

```

Replace "@TCL\_SHELL@" with the path for tclsh, "@TCL\_WISH@" with the path for wish and "@prefix@" with the path for libsimulavr.so.

And the same for the beginnig of gui.tcl:

```

#! @TCL_WISH@

# configuration area

set installPrefix "@prefix@"

# end configuration area

package require Itcl

namespace import itcl::*

...

```

Now you're prepared to run the TCL examples.

### TCL Anacomp Example

#### Note

You must have installed the ITCL extension for TCL/TK to run this example!

This is Klaus' very nice original example simulation.

To build the avr program go to examples/anacomp directory:

> avr-gcc -g -02 -mmcu=at90s4433 -o main.elf main.c

After performing the build you can start the simulation:

> ../simulavr.tcl -d at90s4433 -f main.elf -u -s anacomp.tcl

This starts a simple gui and enables the user to enter analog values (0.0 .. 5.0) in the input fields. After entering a new analog value in ain0 or ain1, you must press the update button!

At this point, the output of the analog comparator will be used to determine the output state of the "->B0" field. "->B0" displays the state of the Port B 0 pin. Its value is determined by the following logic:

• if ain0 > ain1 B0 = H(igh)

- if ain0 == ain1 B0 = L(ow)

- if ain0 < ain1 B0 = L(ow)

And not to forget, you can run this simulation together with gdb debugger or also ddd:

```

> tclsh ../simulavr.tcl -d at90s4433 -f main.elf -u -s anacomp.tcl -g

```

The one and only difference to the simulation command before is the "-g" option!

### LCD and SerialRx, SerialTx Example

#### Note

You must have installed the ITCL extension for TCL/TK to and ddd to run this example!

This example is written by Knut Schwichtenberg and based on Klaus' Anacomp Example and uses the avr-libc example stdiodemo to display characters on the LCD.

First we build the avr program. Go to examples/stdiodemo directory:

Then we have to prepare a tcl file too (in the same way as described before), copy and edit checkdebug.tcl:

```

#! @TCL_WISH@

# configuration area

set WishCMD "@TCL_WISH@"

set DDDCMD "@DDD@"

set installPrefix "@prefix@"

```

And now you can start:

```

> wish ./checkdebug.tcl

```

The following commands are taken from the LCD-specific examples/stdiodemo/checkdebug.tcl script:

Lcd mylcd \$ui "lcd0" ".x"

sc AddAsyncMember mylcd

The first command creates a LCD instance mylcd with the name lcd0 The second command adds the LCD instance to the simulavr timer subsystem as an asynchronous member. Asynchronous Timer objects are updated every 1ns - which means every iteration in the simulavr main-loop. All timing is done internally in the lcd.c. The rest of this simulation script is the normal business create Nets for each LCD pin, wire the Nets to the CPU pins. The stdiodemo application contains a serial receiver and transmitter part to receive commands and interpret it and if possible prints it on the LCD or sends a response to the serial receiver. Transmitter and receiver application are implemented by polling opposite to the Keyboard example. The components used for the SerialRx/Tx are described below. Together with the comments in the script you should be able to understand what happens. Please mind the different names for the functions SetBaudRate and GetPin for SerialRx and SerialTx! Not optimal but that's it at the moment...

And you can try to simulate it with gdb or ddd:

## Keyboard and SerialRx Example

#### Note

You must have installed the ITCL extension for TCL/TK to run this example!

This example is written by Knut Schwichtenberg and based on Klaus' Anacomp Example and uses the Atmel application note AVR313 to convert the incoming data from the keyboard into a serial ASCII stream and sends this stream via the serial interface. Atmel's C-Code is ported to a current avr-gcc (4.x) and a Mega128. For this example only the serial transmitter is used. Atmel implemented the serial transmitter as interrupt controlled application, opposite to the serial transmitter / receiver of the LCD example. Here a polled solution is implemented.

To build the avr program go to examples/atmel\_key directory:

```

> avr-gcc -g -mmcu=atmega128 -I. -DF_CPU=4000000UL -0s \

-funsigned-char -funsigned-bitfields -fpack-struct \

-fshort-enums -Wall -Wstrict-prototypes -o atmel_key.elf \

kb.c main.c serial.c StdDefs.c -lm

```

More examples

After performing the build you can start the simulation:

```

> ../simulavr.tcl -d atmega128 -f atmel_key.elf -u -F 250 \

-s atmel key.tcl

```

This example by itself is good to show how the GUI needs to be setup to make the Keyboard component work. The output of the keyboard is displayed into SerialRx component. Let's look into the simulation script to point out some details:

Keyboard:

```

Keyboard kbd $ui "kbdl" ".x"

Keyboard_SetClockFreq kbd 40000

sc Add kbd

```

These three commands create a Keyboard instance kbd with the name "kbd1". For this instance the clock timing is set to 40000ns. simulavr internal timing for any asynchronous activity are multiples of 1ns. The third command adds the keyboard instance to the simulavr timer.

Create a CPU AtMega128 with 4MHz clock. Create indicators for the digital pins (not necessary but good looking). Create a Net for each signal - here Clock(key\_clk), Data(key\_data), Run-LED(key\_runLED), Test-Pin(key\_TestPin), and Serial Output(key\_txD0). Wire the pins Net specific. Run-LED and Test-Pin are specific to the Atmel AP-Note AVR313. The output of the keyboard converter is send to the serial interface. Based on an "implementation speciality" of simulavr a serial output must be either set by the AVR program to output or a Pin with a Pull-Up activated has to be wired.

SerialRx:

```

SerialRx mysrx $ui "serialRx0" ".x"

SerialRxBasic_SetBaudRate mysrx 19200

```

These two commands create a SerialRx instance mysrx with the name "serialRx0". For this instance the baud rate is set to 19200. This SerialRx is wired to the controller pin, a display pin by the following commands:

```

ExtPin exttxD0 $Pin_PULLUP $ui "txD0" ".x"

key_txD0 Add [AvrDevice_GetPin $dev1 "E1"]

key_txD0 Add exttxD0

key_txD0 Add [SerialRxBasic_GetPin mysrx "rx"]

```

The last command ExtPin shows an alternative default value for txD0-Pin. Here it is pulled high - what is identical of adding any pull-up resistor to the device pin - no matter which resistor value is used.

While creating this example, simulavr helped to find the bugs left in the AP-Note.

### atmega128\_timer example

This example uses Timer 2 on the ATMega128 to generate a periodic interrupt. It prints 1 to 500 as the number of ticks increases. It's not a dedicated tcl example, but shows, that you can use :file:`simulavr.tcl` in the same way as the original simulavr program.

To build the avr program go to examples/atmega128\_timer directory:

After performing the build you can start the simulation with simulavr:

> simulavr -d atmega128 -f timer.elf -W 0x20,- -R 0x22,- -T exit

```

or with simulavr.tcl:

```

> tclsh ../simulavr.tcl -d atmega128 -f timer.elf -W 0x20,- -R 0x22,- -T exit

#### atmega48 example

Demonstrates the ATMega48 and following Stimulation classes:

- HWAdmux with additional pin inputs for not GPIO port support.

- SpiSink monitors the /SS, SCLK and MISO pins and prints each byte to stdout.

- SpiSource drives the /SS, SCLK and MOSI pins with data from the spidata file.

- PinMonitor monitors Port A Bit 0 and prints changes in its binary status to stdout.

- AdcPin Stimulates Port F Bit 0 with the values contained in the anadata{1,2,3} files.

The AVR program alternately (every other byte) echoes the byte received on the SPI or the ADCH value read from a recenet A/D converter, to the SPI. Also, the value from the A/D converter rotates through the values at the pins PC5, ADC6, and ADC7.

The spidata file contains an HDLC encoded stream of mostly flags that was used in my project at work. (We're running a form of PPP/HDLC over SPI.)

The format of the spidata file consists of comments (lines that start with a '#') and data lines. Each data line consists of 3 values.

- First Value the value (0 or non-zero)of /SS

- Second Value the value (0 or non-zero) of SCLK

- Third Value the value (0 or non-zero) of MOSI

When the SpiSource program stimulator reaches the end-of-file, it rewinds and repeats ad-nauseum.

The anadata{1,2,3} files contains analog data that that is read by the AdcPin class and written to the Port C Bit 5, ADC6 and ADC7 analog inputs of the ATMega48.

The format of the anadata{1,2,3} files consists of comments (lines that start with a '#' character) and analog input lines. Each input line consists of 2 values separated by whitespace.

- First Value number of nano-seconds before the next value is read and applied to the analog input.

- Second Value signed integer "analogValue" to be applied to the analog input.

To try it:

#### Step 1:

Build the AVR test program in examples/atmega48 directory:

> avr-gcc -g -mmcu=atmega48 -0s -o atmega48.elf main.cpp

#### Step 2:

Prepare check.tcl in the same way as in other TCL examples before:

```

#! @TCL_WISH@

# configuration area

set installPrefix "@prefix@"

# end configuration area

#load the avr-simulator package

load ${installPrefix}/libsimulavr.so

```

Replace the pathes for wish and the install path for libsimulavr.so

#### Step 3:

Run the test TCL script from this directory:

> wish check.tcl

#### Step 4:

Marvel at the stdio activity.

#### Step 5:

Try modifying the spidata file and see the results.

What you'll see on stdout:

Note: Comments added on the right.

| spisink:  | /SS negated  | ; | SPI /SS goes HIGH (printed by SpiSink)                               |

|-----------|--------------|---|----------------------------------------------------------------------|

| spisink:  | /SS asserted | ; | SPI /SS goes LOW (printed by SpiSink)                                |

| spisink:  | 0x7E         | ; | echoed HDLC Data from AVR on SPI MISO                                |

| spisink:  | 0x66         | ; | Analog Data from AVR PC5 as decoded on SPI MISO                      |

| spisink:  | 0x02         | ; | echoed HDLC Data from AVR on SPI MISO                                |

| spisink:  | 0x33         | ; | Analog Data from AVR ADC6 as decoded on SPI MISO                     |

| spisink:  | 0xD3         | ; | echoed HDLC Data from AVR on SPI MISO                                |

| spisink:  | 0x28         | ; | Analog Data from AVR ADC7 as decoded on SPI MISO                     |

| spisink:  | 0x7E         | ; | echoed HDLC Data from AVR on SPI MISO                                |

| spisink:  | 0x23         | ; | Analog Data from AVR PC5 as decoded on SPI MISO                      |

|           |              |   |                                                                      |

|           |              |   |                                                                      |

| spisink:  | 0x7E         | ; | echoed HDLC Data from AVR on SPI MISO                                |

| spisink:  | 0x04         | ; | Analog Data from AVR {PC5,ADC6, ADC7} as decoded on SPI MISO         |

| PORTBO: N | IEGATE       | ; | Port B Bit 0 (interrupt output) set high by AVR (printed by PinMonit |

|           |              |   |                                                                      |

|           |              |   |                                                                      |

|           |              |   |                                                                      |

#### feedback example

This example illustrates how one can provide a program external to the simulated AVR which provides "feedback" to the simulated program. A feedback program can interact with the AVR hosted program just like devices would in the "real world."

This example is certainly a primitive example of this but it illustrates the principle. The application writes the following lines to UARTO:

hello world #1 hello world #2 hello world #3 hello world #1

The initial input value of ADC0 is 0. When the feedback modules sees 1, 2 or 3, it changes the "voltage" on ADC0. The debug output expected is:

ADC0=10 expect 10 ADC0=20 expect 20 ADC0=30 expect 30 ADC0=10 expect 10

To build the avr program go to examples/feedback directory:

> avr-gcc -g -mmcu=atmega128 -DF\_CPU=4000000UL -Os \

-o feedback.elf main.c debugio.c uart.c adc.c

Prepare simfeedback.tcl in the same way as in other TCL examples before:

```

#! @TCL_SHELL@

package require Itcl

namespace import itcl::*

```

Replace the path for tclsh. If this is done, you can start the simulation with simulavr.tcl:

```

> tclsh ../simulavr.tcl -d atmega128 -f feedback.elf -s feedback.tcl \

-W 0x20,/dev/stderr -R 0x22,- -F 4000000 -T exit -S simfeedback.tcl

```

### **Python examples**

This are some examples to demonstrate usage of pysimulavr. You need to build python simulavr module named pysimulavr. Maybe you have installed the pysimulavr debian package, then you can test it:

> python3

>>> import pysimulavr

>>>

If this works without a error message, then the python module is ready.

If not, e.g. you want to run the tests against the module, you have to build just before, then you can give the environment variable PYTHONPATH with the path to \_pysimulavr.so and pysimulavr.py in the same line just before the python command:

> PYTHONPATH=<path-to-\_pysimulavr.so> python3 <other-options>

All python examples are to find on examples/python directory. Go there and try it:

#### Simple timer unittest

We have to build the avr program for the simulation:

> avr-gcc -g -mmcu=atmega128 -02 -o example.elf example.c

The program is a modified variant from tcl example atmega128\_timer before. The test is written as a unittest. You can start it by:

> python3 example.py atmega128:example.elf

As result you should see something like this:

```

test_01 (__main__.TestBaseClass)

just run 3000 ns + 250 ns ... ok

test_02 (__main__.TestBaseClass)

just run 2 steps ... ok

test_03 (__main__.TestBaseClass)

check PC and PC size ... ok

test_04 (__main__.TestBaseClass)

check address of data symbols ... ok

test_05 (__main__.TestBaseClass)

access to data by symbol ... ok

test_06 (__main__.TestBaseClass)

write access to data by symbol ... ok

test_07 (__main__.TestBaseClass)

```

```

test toggle output pin ... ok

test_08 (__main__.TestBaseClass)

work with breakpoints ... ok

Ran 8 tests in 0.842s

OK

```

So you can see, how easy it's to write unittests for simulavr or also for your avr code. But you can use pysimulavr also for other things, look at example.py how to use pysimulavr.

#### Connect pins and change state

Shows the usage of Pin and Net. A net connect pins together. Change the output state of one pin will result in changing the input state of the other pins. This can be used as starting point to understand usage of SetOutState/SetInState methods of Pin class and how it works. This is not a real simulation. It demonstrates to use Pin and Net class without a simulation target. You can start it by:

```

> python3 example pin.py

```

You see the following:

```

set vcc=5.00V ...

create 2 pins ...

pin1: (char)pin='L', (bool)pin=0, pin.GetAnalogValue(vcc)=2.75V

pin2: (char)pin='t', (bool)pin=1, pin.GetAnalogValue(vcc)=2.75V

create net ...

add pin1 to net:

<pin1 change: in=L/0.00V, out=L/0.00V>

add pin2 to net:

<pin1 change: in=L/0.00V, out=L/0.00V> <pin2 change: in=L/0.00V, out=t/0.00V>

pin1: (char)pin='L', (bool)pin=0, pin.GetAnalogValue(vcc)=0.00V

pin2: (char)pin='t', (bool)pin=0, pin.GetAnalogValue(vcc)=0.00V

set pin2 output to PULLUP:

<pin1 change: in=L/0.00V, out=L/0.00V> <pin2 change: in=L/0.00V, out=h/0.00V>

pin1: (char)pin='L', (bool)pin=0, pin.GetAnalogValue(vcc)=0.00V

pin2: (char)pin='h', (bool)pin=0, pin.GetAnalogValue(vcc)=0.00V

set pin1 output to HIGH:

<pin1 change: in=H/5.00V, out=H/5.00V> <pin2 change: in=H/5.00V, out=h/5.00V>

pin1: (char)pin='H', (bool)pin=1, pin.GetAnalogValue(vcc)=5.00V

pin2: (char)pin='h', (bool)pin=1, pin.GetAnalogValue(vcc)=5.00V

set pin2 output to TRISTATE:

<pin1 change: in=H/5.00V, out=H/5.00V> <pin2 change: in=H/5.00V, out=t/5.00V>

pin1: (char)pin='H', (bool)pin=1, pin.GetAnalogValue(vcc)=5.00V

pin2: (char)pin='t', (bool)pin=1, pin.GetAnalogValue(vcc)=5.00V

set pin1 output to TRISTATE:

<pin1 change: in=t/2.75V, out=t/2.75V> <pin2 change: in=t/2.75V, out=t/2.75V>

pin1: (char)pin='t', (bool)pin=1, pin.GetAnalogValue(vcc)=2.75V

pin2: (char)pin='t', (bool)pin=1, pin.GetAnalogValue(vcc)=2.75V

set pin2 output to LOW:

```

```

<pin1 change: in=L/0.00V, out=t/0.00V> <pin2 change: in=L/0.00V, out=L/0.00V>

pin1: (char)pin='t', (bool)pin=0, pin.GetAnalogValue(vcc)=0.00V

pin2: (char)pin='L', (bool)pin=0, pin.GetAnalogValue(vcc)=0.00V

```

#### How to control pins

This is a more complex example. It demonstrates, how you can simply watch for pin output changes and how you could inject external pin changes to the simulator to stimulate your program functionality. We build at first the avr program for the simulation:

> avr-gcc -g -mmcu=atmega128 -02 -o example\_io.elf example\_io.c

The program is a modified variant from tcl example atmega128\_timer before.

In this simulation we have a external connection to pin A0, A1 and A7 from port A and set the state of pin A1 and A7 to low or high at a defined simulation time. And we can see, when and how the state of this pin is changed.

You can start the simulation by:

```

> python3 example_io.py atmega128:example_io.elf

```

As result you should see something like this:

```

simulation start: (t=0µs)

simulation end: (t=15000µs)

pin A0

change to 't' at 0µs (dt=0µs)

change to 'L' at 17\mu s (dt=17\mu s)

change to 'H' at 2032µs (dt=2015µs)

change to 'L' at 4032µs (dt=2000µs)

change to 'H' at 6036µs (dt=2005µs)

change to 'L' at 8035µs (dt=1999µs)

change to 'H' at 10034µs (dt=1999µs)

change to 'L' at 12033µs (dt=1999µs)

change to 'H' at 14037µs (dt=2004µs)

pin Al

change to 'H' at Oµs (dt=Oµs)

change to 'L' at 7000µs (dt=7000µs)

change to 'H' at 14000µs (dt=7000µs)

pin A7

change to 'H' at 0µs (dt=0µs)

change to 'L' at 12000µs (dt=12000µs)

value 'timer2 ticks'=7

value 'port val'=0x7e

value 'port cnt'=3

```

#### How to get a more detailed view

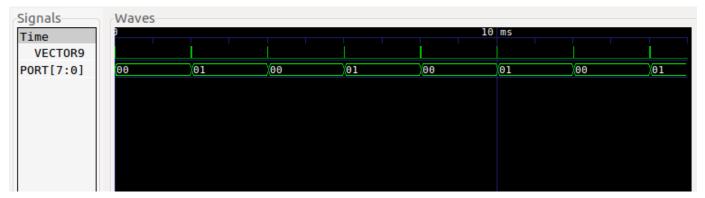

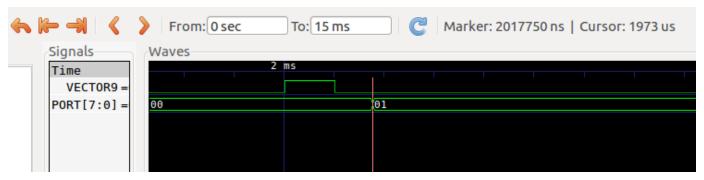

This example is closed to the example before. ex\_pinout.c initialise timer2 in CTC mode for a period of 2ms on 4MHz clock frequency. Example output shows the toggle of pin A0. But we will also write a VCD dump. If you have installed gtkwave you can open this VCD dump file ex\_pinout.vcd with gtkwave. So you can compare time written out by this example with the results shown in gtkwave. The signal IRQ.VECTOR9 in VCD dump shows when and how long the ISR was running! First build the avr program:

> avr-gcc -g -mmcu=atmega128 -02 -o ex\_pinout.elf ex\_pinout.c

Then start it by:

> python3 ex\_pinout.py atmega128:ex\_pinout.elf

Output is:

```

port A.0 set to 't' (t=0ns)

port A.0 set to 't' (t=0ns)

simulation start: (t=0ns)

port A.0 set to 'L' (t=10750ns)

port A.0 set to 'L' (t=11000ns)

port A.0 set to 'H' (t=2017750ns)

port A.0 set to 'H' (t=4018000ns)

port A.0 set to 'L' (t=4018000ns)

port A.0 set to 'L' (t=8015750ns)

port A.0 set to 'L' (t=8015750ns)

port A.0 set to 'L' (t=10016250ns)

port A.0 set to 'L' (t=12016500ns)

port A.0 set to 'H' (t=14017000ns)

simulation end: (t=15000000ns)

value 'timer2_ticks'=7

```

And now (if you have installed gtkwave) you can view the traced waveforms:

> gtkwave -a ex\_pinout.sav ex\_pinout.vcd

The full view:

Let's look on a detail. You can see, how long the interrupt procedure was running and when the port value was changed. Compare it with the print out on standard out before! (in picture the value for "Marker:")

### Multicore example

This example demonstrates using python interface for multicore simulation. We simulate 2 ATmega16 cores:

| +      | ++  |     |        |    |

|--------|-----|-----|--------|----|

| Core A | PB3 | PD2 | Core B |    |

| 4MHz   | >-  |     | 10MHz  | Ì  |

|        |     |     |        |    |

| +      | -+  | +-  |        | -+ |

Core A runs as a 250Hz clock generator on pin B3. B3 from core A is conected with pin D2 on core B. Core B counts now all rising edges on pin D2 and measures the time distance between 2 events with timer T0.

This example shows:

- how to use python interface

- how it is possible to run a multicore simulation, in this example also with different clock sources for the cores

- how to connect pins between cores

- how to access global variables, how to get address for a global variable and how to read RAM values from a address

Build the 2 avr programs:

```

> avr-gcc -g -mmcu=atmega16 -02 -DDUAL_A=1 -o multicore_a.elf multicore.c

> avr-gcc -g -mmcu=atmega16 -02 -DDUAL_B=1 -o multicore_b.elf multicore.c

```

And run the simulation:

> python3 multicore.py

Resulting output should then look like:

```

multicore example:

create core A ...

create core B ...

connect core A with core B ...

core B: address(cnt_irq)=0x61

core B: address(cnt_res)=0x61

run simulation ...

t= 4ms, cnt_irq=1, cnt_res= 78

t= 8ms, cnt_irq=2, cnt_res=156

t=20ms, cnt_irq=5, cnt_res=157

t=32ms, cnt_irq=8, cnt_res=156

```

#### ADC example

A example to simulate analog input and how to simulate adc conversion. Build avr program and run the simulation:

```

> avr-gcc -g -mmcu=atmega16 -02 -o adc.elf adc.c

> python3 adc.py atmega16:adc.elf

```

The output shows:

```

before simulation start:

value 'adc_value'=43690 (before init)

aref set to 2.5V

a0 set to 0.3V, this will expect an converted adc int value=122

simulation start: (t=0ns)

```

```

run till main function ...

simulation main entrance: (t=24250ns)

value 'adc_value'=5555 (after init)

simulation break: (t=144250ns)

value 'conversions'=1

value 'adc_value'=122 (simulation break)

simulation end: (t=474250ns)

value 'conversions'=6

value 'adc_value'=122 (simulation end)

```

## **Verilog examples**

To use this examples you have to build simulavr together with the verilog extension. See here how to make it. You can find the example files in examples/verilog directory. Further, if you want to see the waveform you need the gtkwave program. It's a program to display digital waveforms.

#### baretest example

First compile and link avr program:

```

> avr-gcc -mmcu=at90s4433 -0s -o toggle.elf toggle.c

```

Then compile and run the verilog source file:

> iverilog baretest.v -s test -v avr.v -o baretest.vvp > vvp -M<path-to-avr.vpi-directory> -mavr baretest.vvp

Replace <path-to-avr.vpi-directory> to the directory, where your avr.vpi is situated. (could be, for example, in <root-of-repository>/build/libsim) This will create a file baretest.vcd. And if you now start gtkwave, you can see the result:

```

> gtkwave -a baretest.sav baretest.vcd

```

What this example do?

This is the code:

```

int main() {

DDRB = 1;

while(1) {

PORTB = 1;

PORTB = 0;

}

}

```

It sets port B pin 0 to output and start a endless loop toggeling pin 0 at port B. And the result is:

| 🔏 🖶 📋 🛛 🗗 🖃 📥                       |               | 🛛 🔾 🔰 From: <u>0 sec</u> To: <u>100002 ns</u> 🛛 🥑 Marker: 481 | 10 ns   Cu |

|-------------------------------------|---------------|---------------------------------------------------------------|------------|

| ▼ SST                               | Signals       | ls Waves                                                      | 10         |

| L 🚠 test                            | Time<br>clk=1 |                                                               | 10 us      |

|                                     | pb0 =0        |                                                               |            |

| Type Signals                        |               | Ξ.                                                            |            |

| Filter:       Append Insert Replace |               |                                                               |            |

## loop example

Steps are the same as before for baretest example:

```

> avr-gcc -mmcu=attiny2313 -Os -o loop.elf loop.c

> iverilog loop.v -s test -v avr.v avr_ATtiny2313.v -o loop.vvp

> vvp -M<path-to-avr.vpi-directory> -mavr loop.vvp

```

The code is similar to toggle.c but with a twist:

```

int main() {

DDRB = 0xff;

PORTB = 1;

while(1) {

PORTB = PINB << 1;

}

}</pre>

```

Lets see the result:

| > gtkwave -a loop.sav loop.vcd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Image: State of the state | Signals<br>Time<br>clk<br>PB[7:0] | From:         0 sec         To:         100 us         C         Marker:         –           Cursor:         18300 ns           Waves         10 us         20 us         10 us         20 us         10 |  |  |  |

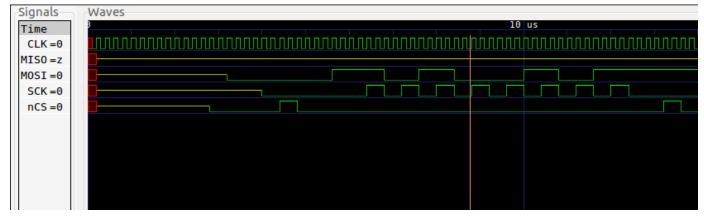

### spi waveform examples

A more complicated example: send data via spi:

```

> avr-gcc -mmcu=atmega8 -Os -o spi-waveforms.elf spi-waveforms.c

```

```

> iverilog spi-waveforms.v -s test -v avr.v avr_ATmega8.v -o spi-waveforms.vvp

```

```

> vvp -M<path-to-avr.vpi-directory> -mavr spi-waveforms.vvp

```

```

> gtkwave -a spi-waveforms.sav spi-waveforms.vcd

```

And we can see the spi signals (just the first byte sequence) in gtkwave:

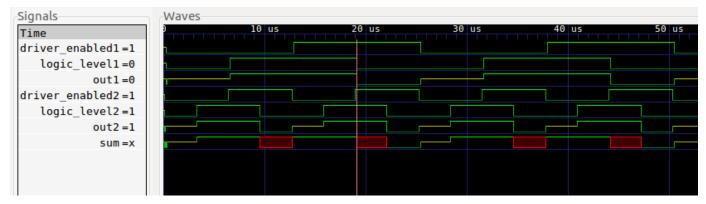

And a second example where data will be send out from controller and received by controller:

```

> avr-gcc -mmcu=atmega8 -Os -o spi.elf spi.c

```

```

> iverilog spi.v -s test -v avr.v avr_ATmega8.v -o spi.vvp

```

- > vvp -M<path-to-avr.vpi-directory> -mavr spi.vvp

- > gtkwave -a spi.sav spi.vcd

And the simulation result:

| Signals        | Waves                                                  |             |

|----------------|--------------------------------------------------------|-------------|